作者:

Lyubomir Kerachev, Yves Lembeye, Jean-Christophe Crébier (Grenoble Electrical Engineering Laboratory)

Christoph Daedlow (Finetech GmBH & Co. KG)

摘要:

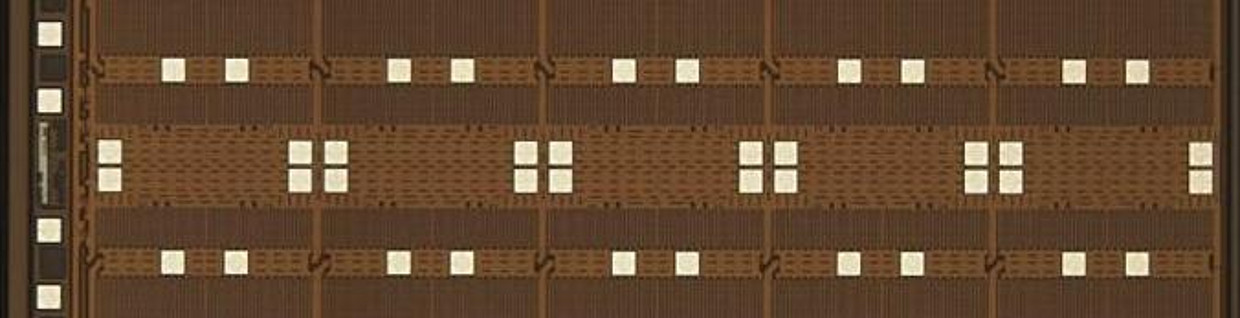

传统的集成电路封装工艺正面临I/O数量越来越多,成本越来越高,引线电阻和寄生电感也随之增加的问题。倒装芯片键合工艺能显著减小芯片的封装尺寸,降低组装成本,减少引线电阻和寄生电感等负面影响。此外,它减少了芯片与作为主要散热途径的基板之间的热界面数量。本文研究了多种微组装技术,如各向异性胶粘接技术、热压焊接技术、热超声焊接技术和焊料粘接技术。同时包括了采用焊球凸点的倒装焊接技术,并对其进行了实验表征。此次工作的目的在于用最适合的倒装芯片键合工艺来完成多引脚,复杂图形的CMOS电路封装。